- XILINX VIVADO DOWNLOAD BITSTREAM GENERATOR

- XILINX VIVADO DOWNLOAD BITSTREAM SOFTWARE

- XILINX VIVADO DOWNLOAD BITSTREAM DOWNLOAD

If developers plan to create their own custom carrier card, they will need to first go through the custom carrier card flow before generating their design through the Vitis or Vivado based tool flows. The following is a decision tree to help guide developers through appropriate workflows: The choice of flow depends on HW target definition, where the target design intersects with Xilinx’s released reference designs, and tool preference. Based on the scope of hardware and design change there are four different flows developers can leverage when developing a custom application. Pleaseĭevelopers may only need to touch parts of the flow to put their own applications on SOM. Tool Requirements to Generate PL Portion of Application ¶Īfter you understand the SOM developer flow (shown below), you can refer to the following table for tool requirements to generate PL portion of your applications. Kv260-vitis git repository, which contains KV260 Vitis platforms, Vitis overlay projects, and their associated Makefiles.

XILINX VIVADO DOWNLOAD BITSTREAM DOWNLOAD

Download the latest SOM Starter Kit BSP from the SOM Wiki XSCT (will be installed as part of Vivado or Vitis)

XILINX VIVADO DOWNLOAD BITSTREAM GENERATOR

For versions 21.2 and lower, apply the Y2K22 patchĭevice Tree Generator (DTG) and Device Tree Compiler (DTC) installation, refer to Build Device Tree Blob Vivado tools installation (if Vitis is not required and installed) Vitis tools installation (this will include Vivado) Please refer to various tool flow sections before determining which tools to install: This document assumes you are using Xilinx tools 2021.1 or higher.ĭepending on the scope of customization and selected workflow, different tools will be needed.

Below is the tool flow that Xilinx uses to generate reference designs for Kria SOM. Developers can use the same generalized flows when creating platforms and designs for their own custom carrier card. Developers can leverage Xilinx provided Kria Vitis platforms that align to a given CC or they can create their own Vitis platform. Vitis provides a design abstraction for provided “Vitis platforms” in which a subset of CC physical interface peripherals is defined and developers can focus on generating an acceleration “overlay” within the context of that platform. Developers can use Vivado to generate a custom HW design which may include a different peripheral configuration set than pre-built Xilinx reference designs. The SOM board files in Vivado captures the hardware configuration of K26 SOM and maps connectivity to Xilinx provided carrier card peripherals.

XILINX VIVADO DOWNLOAD BITSTREAM SOFTWARE

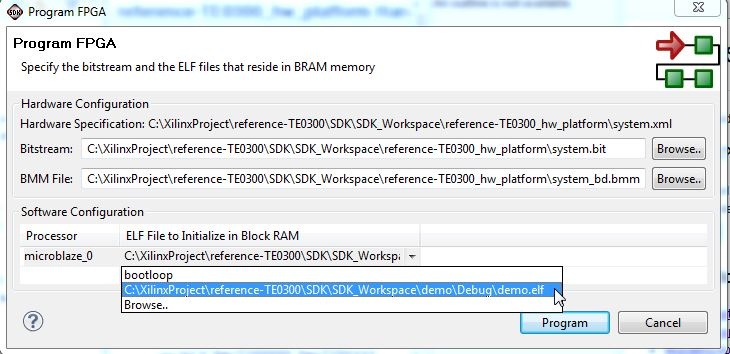

The PL design or bitstream is generated using Vivado and/or Vitis, and it is integrated with Linux software components using PetaLinux. The Kria Starter Kit reference designs have a Linux operating system running in PS, which then runs applications that utilize HW accelerators implemented in PL. The Kria K26 SOM uses the XCK26 Zynq MPSoC chip containing both the Processor Subsystem (PS) and Programmable Logic (PL). The carrier card (CC) can be a Xilinx carrier card (e.g.

The Kria SOM hardware design consist of the SOM (K26) and a carrier card. Whenever available, this document also points to detailed step-by-step tutorials. This document focuses on the overall concept of the different PL hardware generation flows. Use one or more of the Xilinx development tools (such as Vivado™, Vitis™, and PetaLinux) and open source tools (such as Linux Device Tree Generator/Compiler) to build your applications. With Kria SOMs, you can create and test your own custom applications and programmable logic (PL) functions. Kria™ SOM Accelerator and Custom Carrier Card Firmware Development ¶

0 kommentar(er)

0 kommentar(er)